Richard Schroedter, Ahmet Samil Demirkol, Alon Ascoli, Benjamin Max, Florian Nebe, Thomas Mikolajick

12th International Conference on Modern Circuits and Systems Technologies (MOCAST), 28-30 June 2023

Richard Schroedter, Ahmet Samil Demirkol, Alon Ascoli, Benjamin Max, Florian Nebe, Thomas Mikolajick

12th International Conference on Modern Circuits and Systems Technologies (MOCAST), 28-30 June 2023

Eter Mgeladze; Melanie Herzig; Richard Schroedter; Ronald Tetzlaff; Thomas Mikolajick; Stefan Slesazeck

2022 29th IEEE International Conference on Electronics, Circuits and Systems (ICECS), 24-26 October 2022, Glasgow, United Kingdom

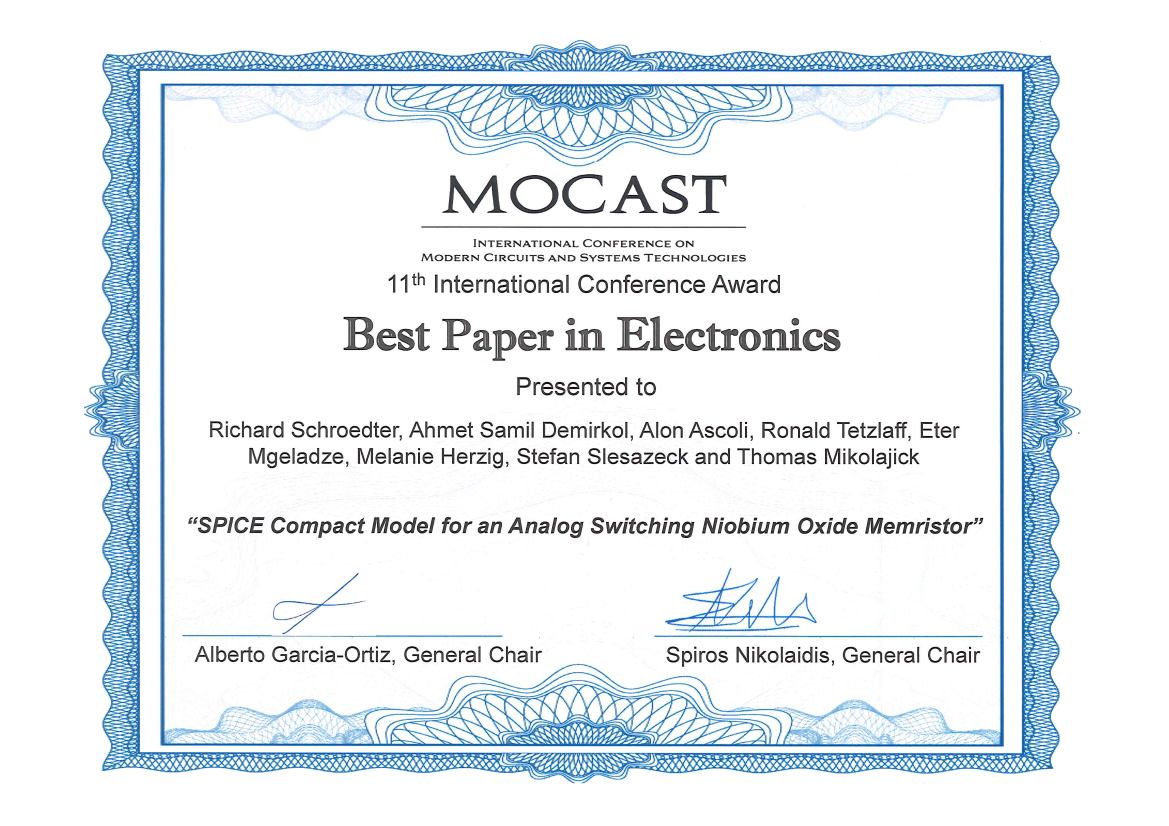

Richard Schroedter; Ahmet Samil Demirkol; Alon Ascoli; Ronald Tetzlaff; Eter Mgeladze; Melanie Herzig; Stefan Slesazeck; Thomas Mikolajick

2022 11th International Conference on Modern Circuits and Systems Technologies (MOCAST), 08-10 June 2022, Bremen, Germany

Richard Schroedter; Eter Mgeladze; Melanie Herzig; Alon Ascoli; Stefan Slesazeck; Thomas Mikolajick; Ronald Tetzlaff

2022 IEEE International Symposium on Circuits and Systems (ISCAS), 27 May 2022 - 01 June 2022, Austin, TX, USA

The crossbar array, which realizes the matrix-vector multiplication (MVM) operation directly employing the Ohm law, represents the central building block of the non-conventional computing-in-memory (CIM) architectures, such as artificial neural networks (ANNs). The MVM is performed in an analog fashion, and, therefore, it is highly desirable to adopt non-volatile analog switching memristors, leveraging, furthermore, their memcapacitive properties.

In this project we aim at the exploitation of the interesting combined memristive and memcapacitive effects in Al2O3 / Nb2O3 based bi-layer device structures, recently developed at NaMLab to be used in conjunction with NFET transistors established at IHM. Based on these devices, we would like to develop a complete design methodology for the implementation of non-conventional versatile computations on a memristive/memcapacitive hardware, which utilizes a hybrid Memristor/Memcapacitor-CMOS architecture, mainly including MVM cores.

For this purpose, the proposed work will cover several essential aspects: (i) realization of cells integrating memristive/memcapacitive devices and NFETs, (ii) experimental and theoretical modelling of the single cells, (iii) system-level modelling, analysis, design, and simulation of the MVM core-based ANNs, (iv) derivation of optimization algorithms, that account for the physical limitations of the hardware realization, (v) set-up of efficient instruction sets and peripheral circuitry design, and (vi) optimized mapping of memcomputing tasks onto the ANN structures. In this way, we expect to gain a comprehensive understanding of the feasibility of adopting the aforementioned device concepts in unconventional computing systems, such as multi-layer perceptrons (MLP), convolutional neural networks (CoNN), and recurrent neural networks (ReNN). Finally, we will investigate the possibility of implementing the Quadratic-Integrate-and-Fire (QIF) neuron model in hardware, and to demonstrate the richness of biomimetic dynamical phenomena, which an array of artificial neural structures of this kind may support.