MemrisTec Seminar 2025 in Leipzig

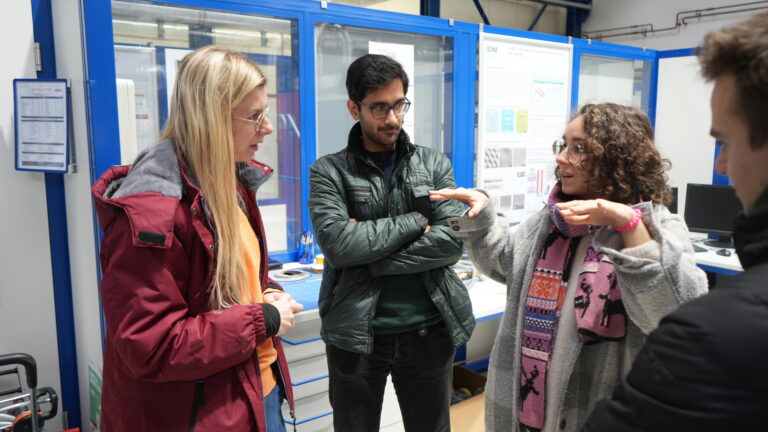

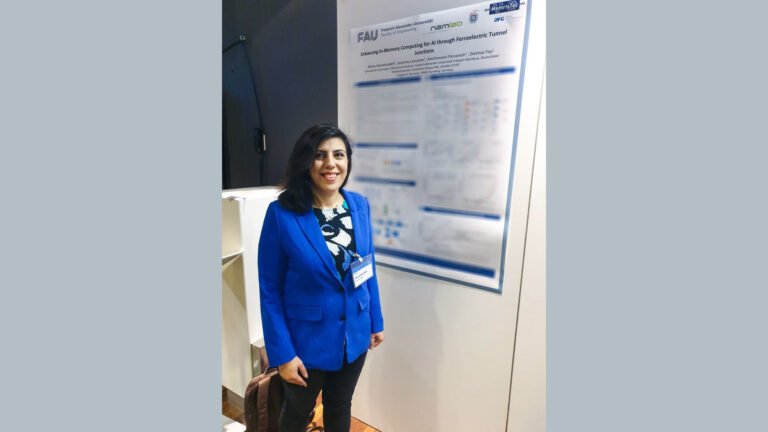

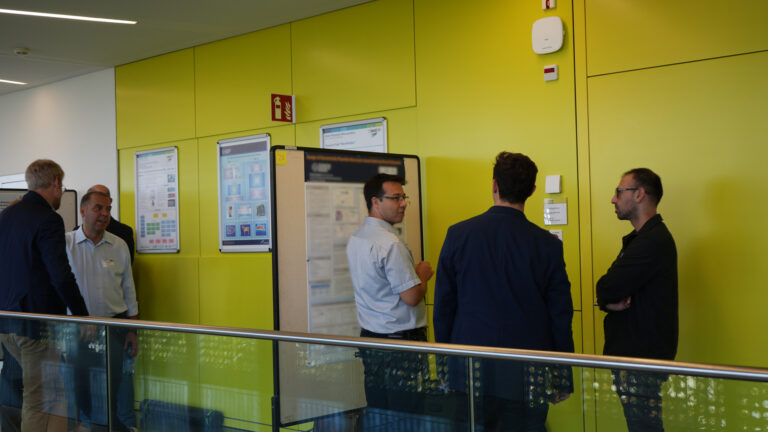

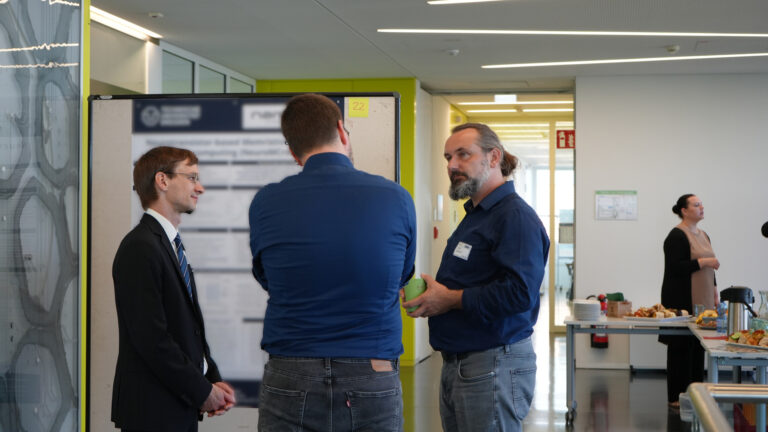

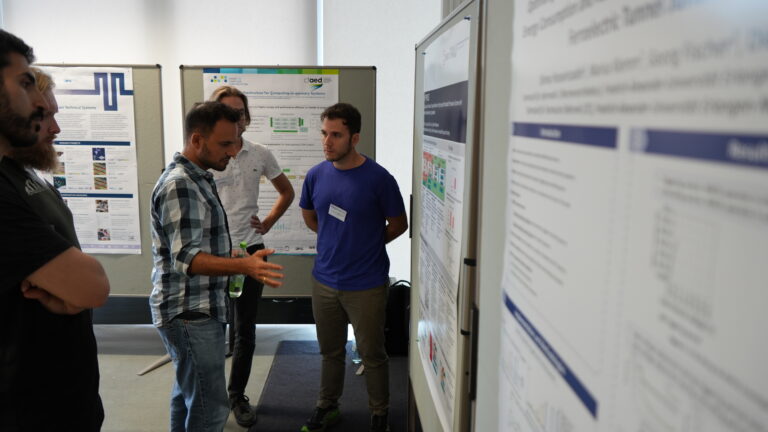

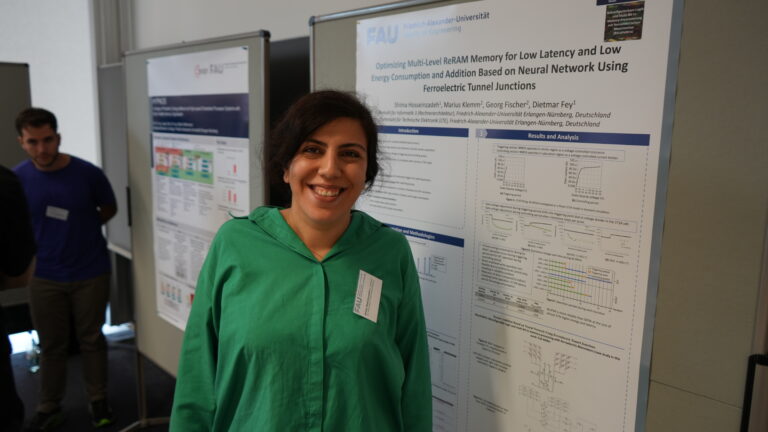

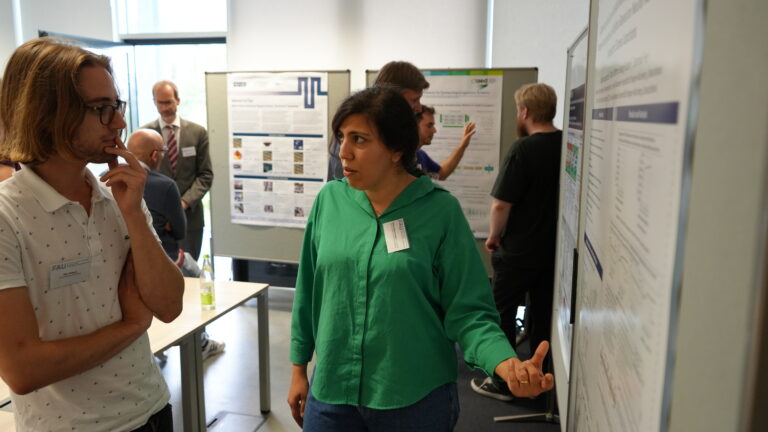

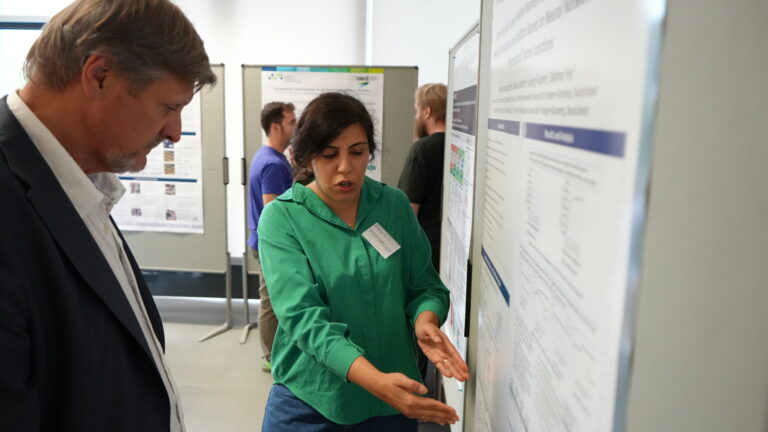

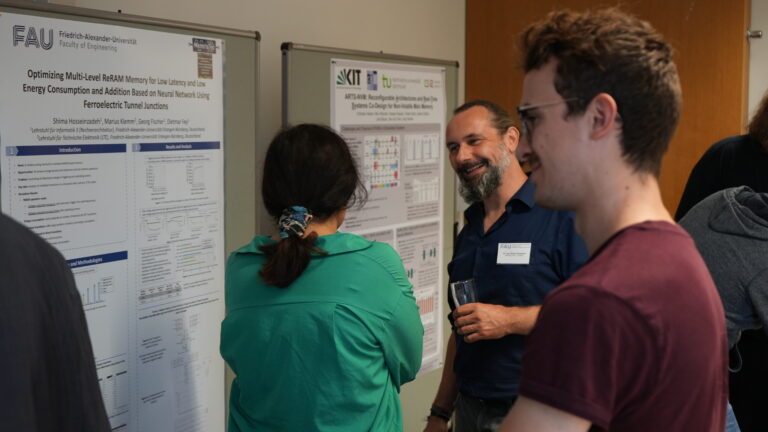

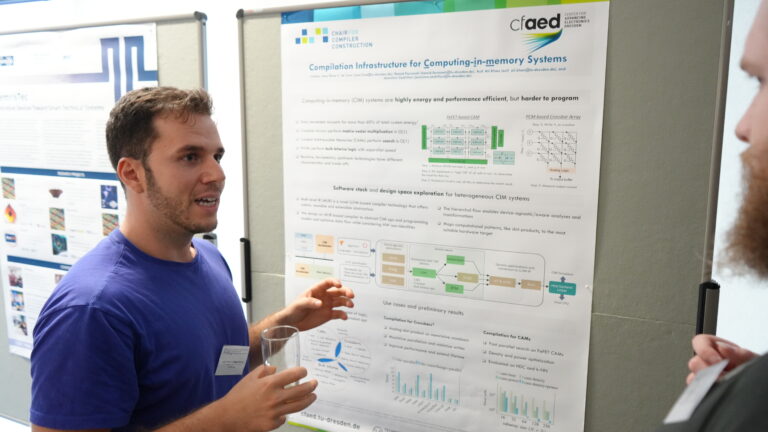

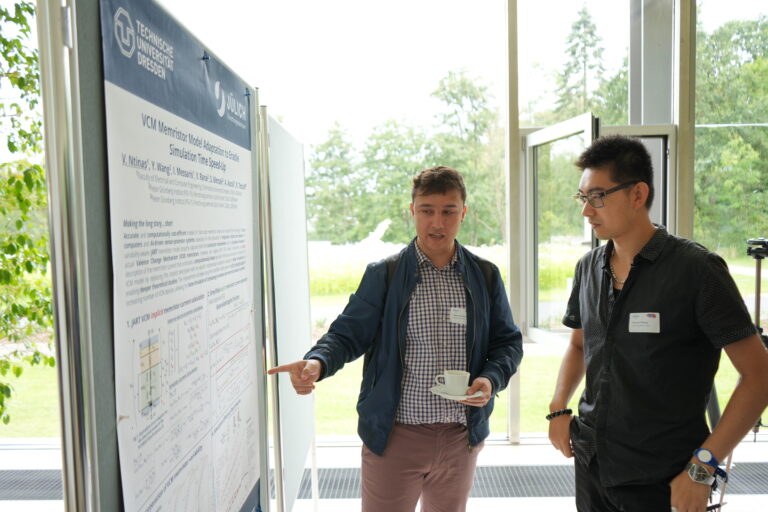

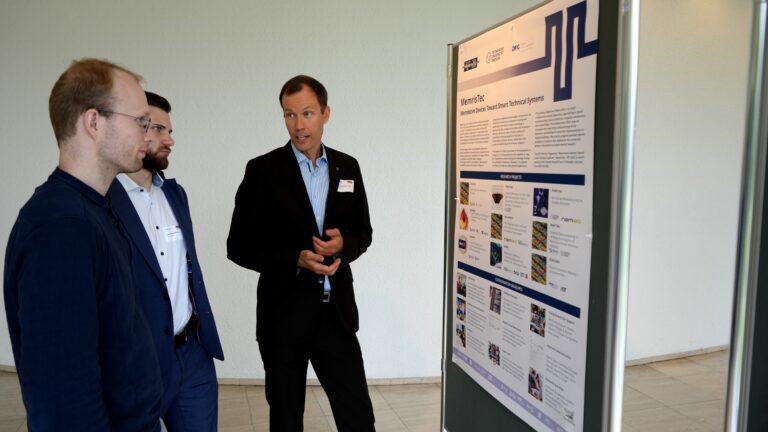

Vom 25. bis 27. November 2025 fand in Leipzig am Leibniz-Institut für Oberflächenverfahrenstechnik (IOM) das MemrisTec-Forschungsseminar 2025 statt. Das Seminar brachte 10 Doktoranden, Masterstudenten und Diplomanden aus dem gesamten MemrisTec-Forschungsprogramm zusammen.

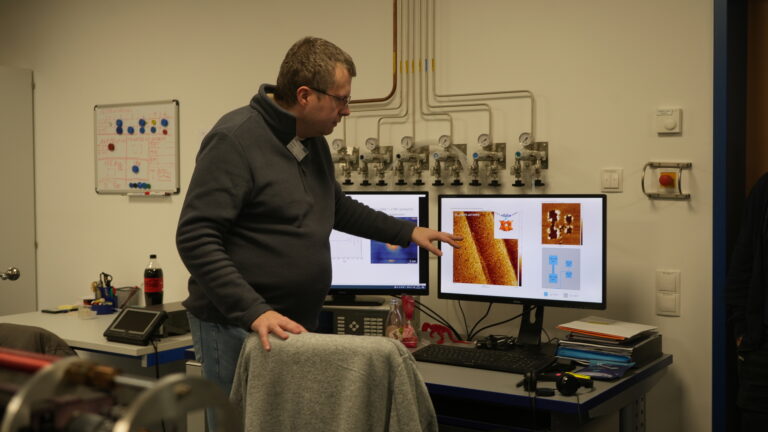

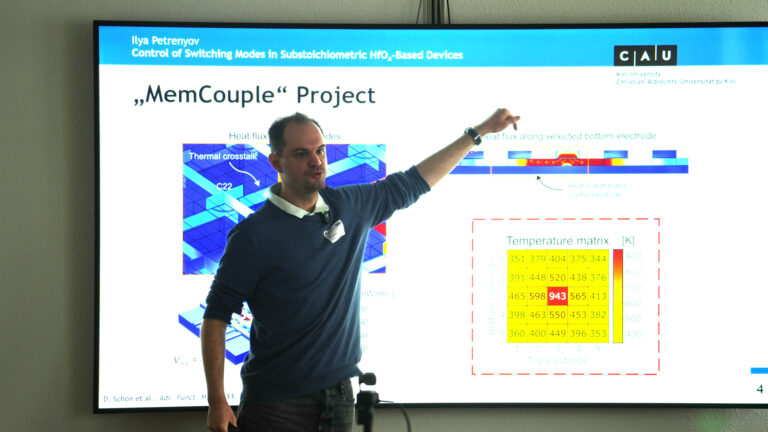

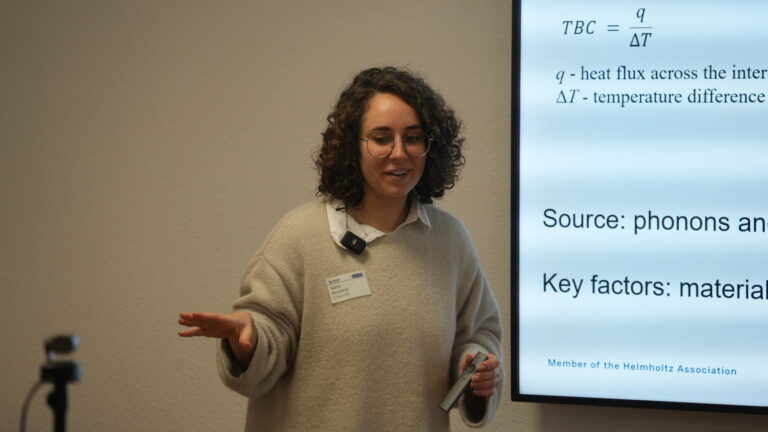

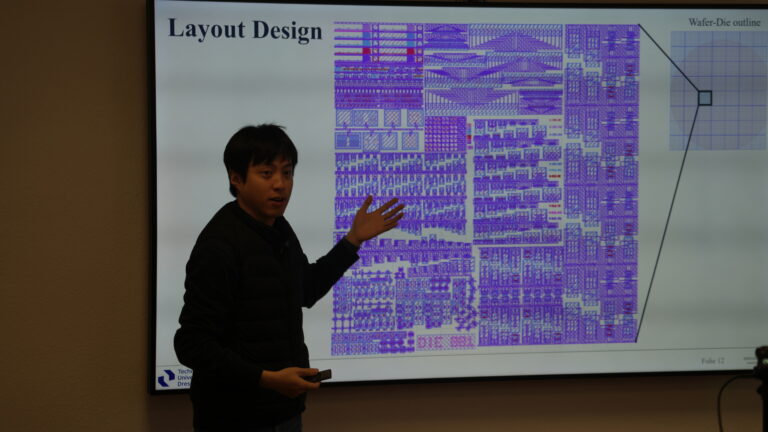

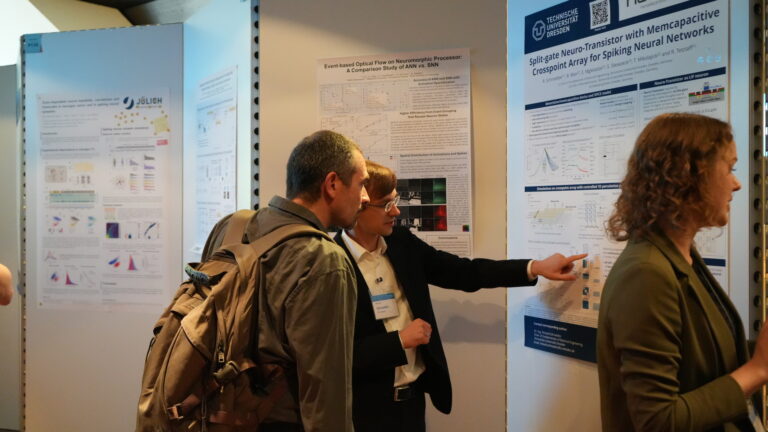

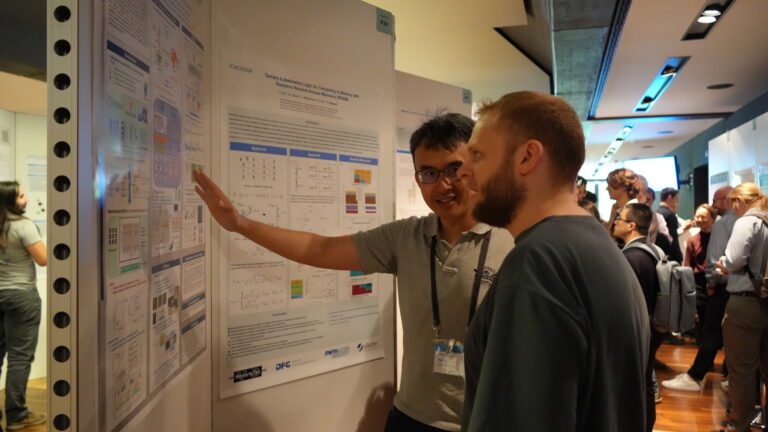

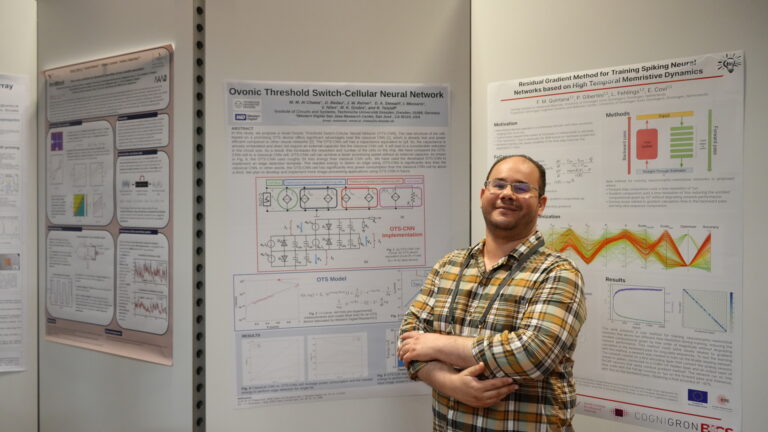

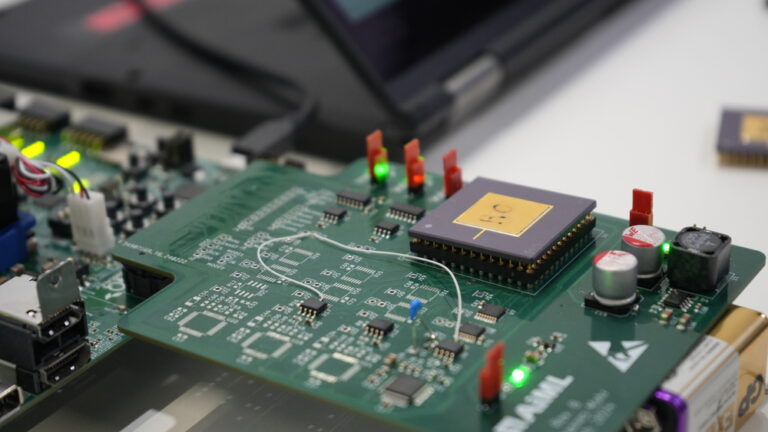

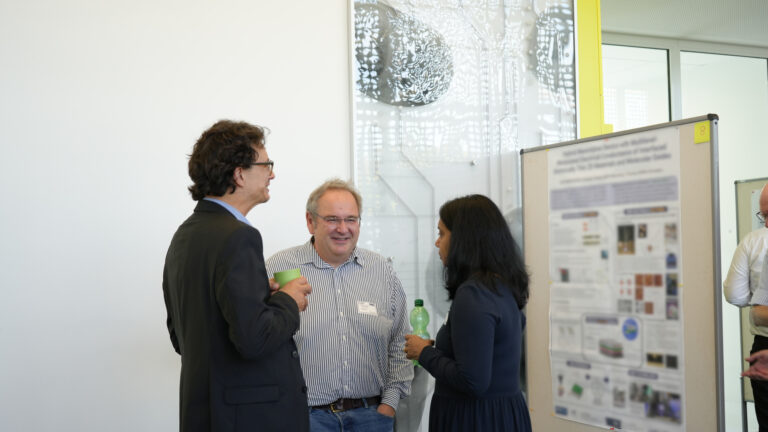

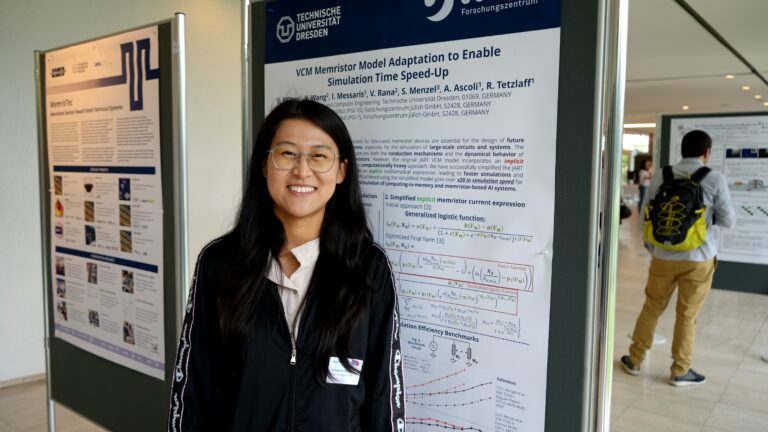

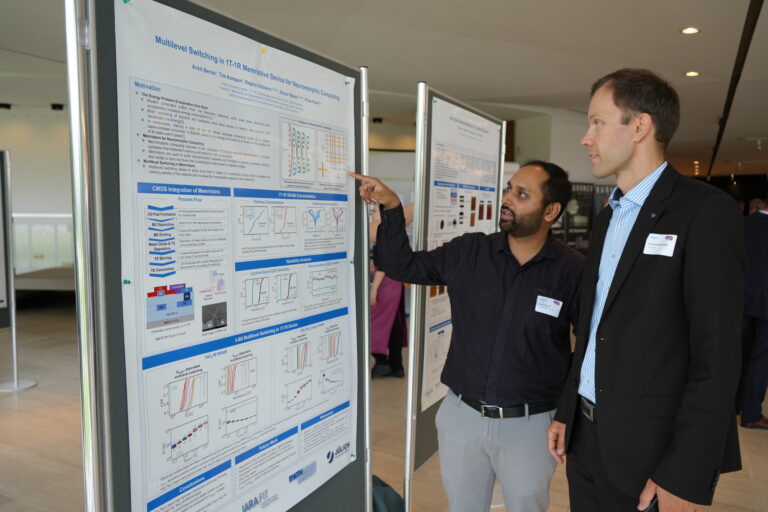

Die Teilnehmer präsentierten den Fortschritt ihrer Abschlussarbeiten und diskutierten ihre Arbeit in einem interdisziplinären Umfeld mit Feedback von Kollegen und erfahrenen Forschern. Auf dem Programm standen außerdem Laborbesichtigungen am IOM und Gastvorträge zu Karrierewegen und der deutschen Forschungslandschaft.

Kirill Monakhov hielt einen Vortrag zum Thema „Ein molekularer chemischer Weg zur Quanteninformationsverarbeitung und zum neuromorphen Rechnen”. Das Seminar bot eine wertvolle Plattform für den Wissensaustausch zwischen den Teilnehmern.

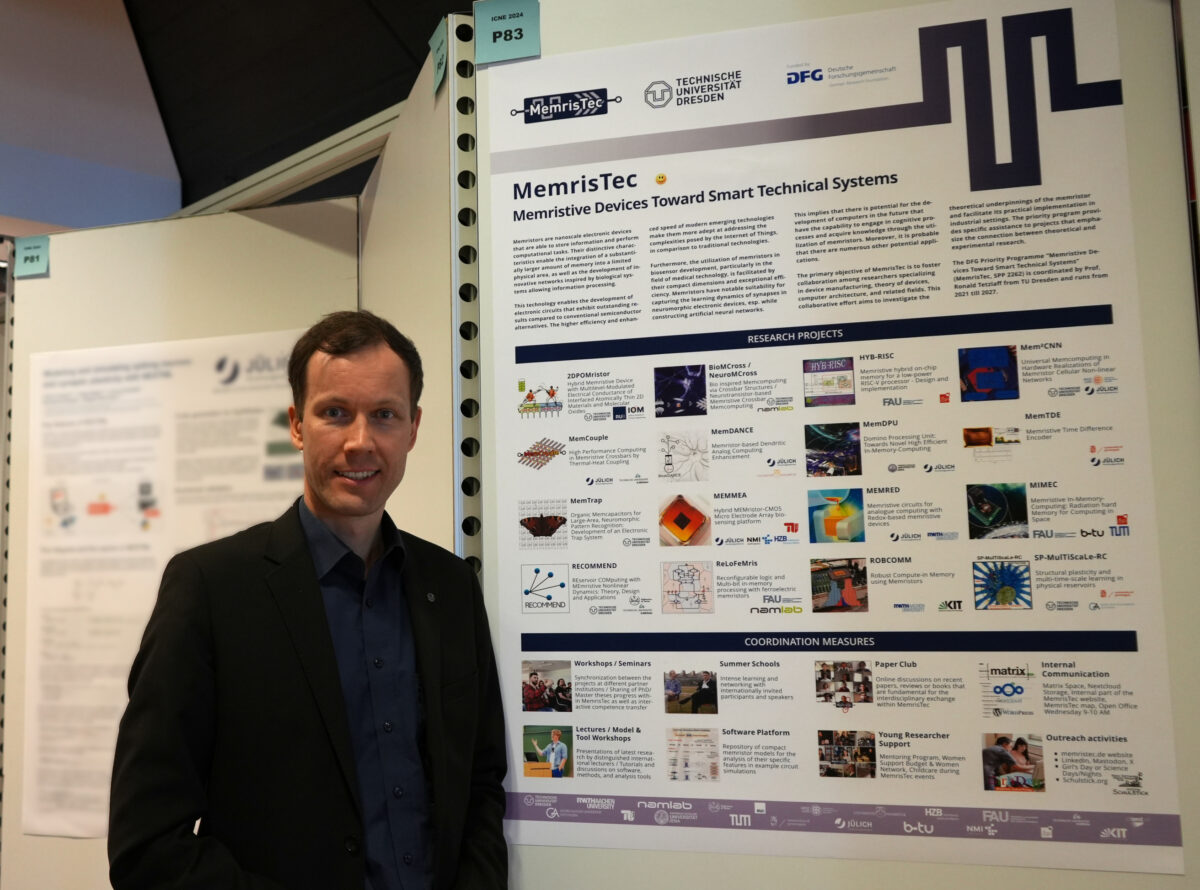

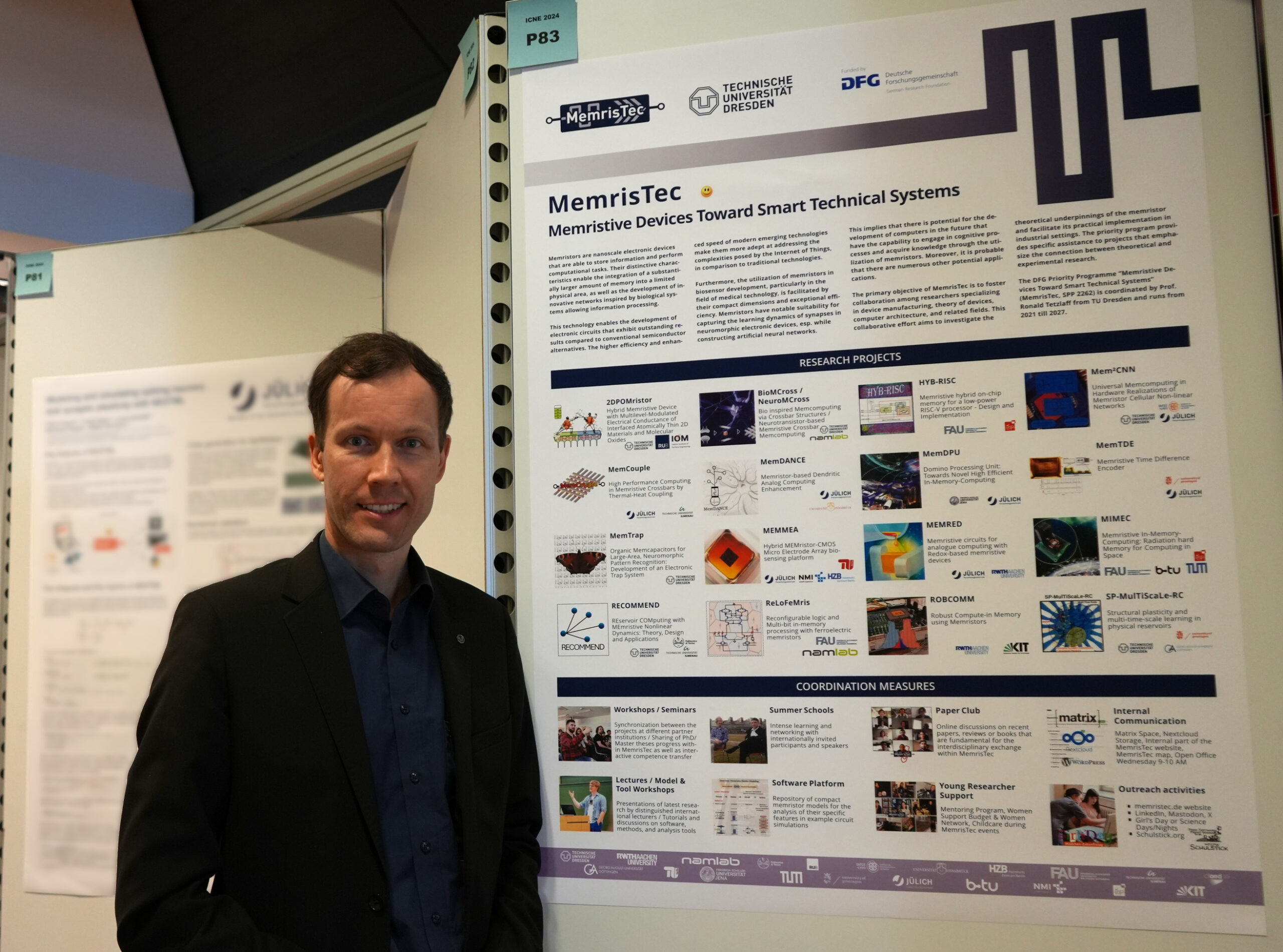

Ein großes Dankeschön von MemrisTec-Koordinator Ronald Tetzlaff von der Technischen Universität Dresden an alle Teilnehmer und die lokalen Organisatoren um Kirill Monakhov vom Leibniz-Institut für Oberflächenverfahrenstechnik in Leipzig, die perfekte Bedingungen für dieses Seminar geschaffen haben.