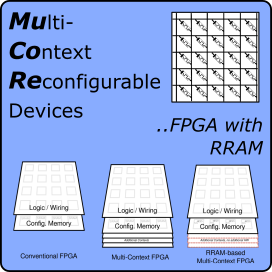

In an era where computing demands are constantly growing, the MuCoRe project is exploring how a single chip could handle multiple hardware configurations simultaneously. Researchers at the University of Rostock and IHP – Leibniz-Institute for Innovative Microelectronics, led by Prof. Marc Reichenbach and Prof. Christian Wenger, are developing multi-context FPGAs (MC-FPGAs) using multi-bit resistive RAM (RRAM) cells as part of the DFG Priority Program MemrisTec. Funded by the DFG starting in 2025, the project aims to combine the speed and flexibility of FPGAs with the efficiency and density of memristive memory.

At the heart of MuCoRe is the multi-level capability of RRAM cells. Each cell can store eight states, supporting up to three hardware configurations per cell and drastically reducing the area and power requirements compared to conventional SRAM-based designs. Specialized analog-to-digital converters (ADCs) provide reliable, energy-efficient readout, and the non-volatile nature of RRAM eliminates the need to maintain inactive configurations.

Beyond individual components, MuCoRe is taking a system-wide approach. The team is using open-source tools and iterative design methods to evaluate critical metrics, including area, power, and performance. By merging analog memristive memory with digital FPGA logic, the project is creating a flexible, energy-efficient computing platform. If successful, MuCoRe could redefine how reconfigurable digital systems are built, providing faster, more adaptable hardware for next-generation applications.